Електронне імпульсне навантаження на базі TL494. Управління силовими транзисторами мікросхемою tl494

Всі електронники, що займаються конструюванням пристроїв електроживлення, рано чи пізно стикаються з проблемою відсутності еквівалента навантаження або функціональною обмеженістю наявних навантажень, а так само їх габаритами. На щастя, поява на російському ринку дешевих та потужних польових транзисторів дещо виправила ситуацію.

Стали з'являтися аматорські конструкції електронних навантажень на базі польових транзисторів, більш придатних до використання як електронний опір, ніж їх біполярні побратими: краща температурна стабільність, практично нульовий опір каналу у відкритому стані, малі струми управління - основні переваги, що визначають перевагу регулюючого компонента у потужних пристроях. Більш того, найрізноманітніші пропозиції з'явилися від виробників приладів, прайси яких рясніють найрізноманітнішими моделями електронних навантажень. Але, оскільки виробники орієнтують свою складну і багатофункціональну продукцію під назвою "електронне навантаження" в основному на виробництво, ціни на ці вироби настільки високі, що покупку може дозволити собі лише дуже заможна людина. Щоправда, не зовсім зрозуміло, - навіщо заможній людині електронне навантаження.

ЕН промислового виробництва, орієнтованого на аматорський інженерний сектор, мною не було помічено. Значить, знову доведеться все робити самому. Е-ех... Почнемо.

Переваги електронного еквівалента навантаження

Чим же в принципі електронні навантажувальні еквіваленти краще традиційних засобів (потужні резистори, лампи розжарювання, термонагрівачі та інші пристрої), що використовуються найчастіше конструкторами при налагодженні різних силових пристроїв?

Громадяни порталу, які стосуються конструювання та ремонту блоків живлення, безсумнівно знають відповідь на це питання. Особисто я бачу два фактори, достатні для того, щоб мати у своїй "лабораторії" електронне навантаження: невеликі габарити, можливість управління потужністю навантаження у великих межах простими засобами(так, як ми регулюємо гучність звучання або вихідна напругаблоку живлення - звичайним змінним резистором, а не потужними контактами рубильника, двигуном реостата і т.д.).

Крім того, "дії" електронного навантаження можна легко автоматизувати, полегшивши таким чином і зробивши витонченішими випробування силового пристрою за допомогою електронного навантаження. При цьому, зрозуміло, звільняються очі та руки інженера, робота стає продуктивнішою. Але про принади всіх можливих наворотів і досконалостей - не в цій статті, і, можливо, від іншого автора. А поки що, - лише про ще один різновид електронного навантаження - імпульсний.

Особливості імпульсного варіанта ЕН

Аналогові електронні навантаження безумовно хороші і багато хто з тих, хто використовував ЕН при налагодженні силових пристроїв, оцінили її переваги. Імпульсні ЕН мають свою особливість, даючи можливість оцінки роботи блоку живлення при імпульсному характері навантаження такому, як, наприклад, робота цифрових пристроїв. Потужні підсилювачі звукових частот так само надають характерний вплив на пристрої живлення, а тому, непогано було б знати, як поведеться блок живлення, розрахований і виготовлений для конкретного підсилювача, при певному заданому характері навантаження.

При діагностиці блоків живлення, що ремонтуються, ефект застосування імпульсної ЕН так само помітний. Так, наприклад, за допомогою імпульсної ЕН було виявлено несправність сучасного комп'ютерного БП. Заявлена несправність даного 850-ватного БП була наступною: комп'ютер при роботі з цим БП вимикався довільно в будь-який час при роботі з будь-яким додатком, незалежно від споживаної, на момент вимкнення, потужності. При перевірці на звичайне навантаження (купа потужних резисторів +3В, +5В і галогенних лампочок по +12В) цей БП відпрацював на "ура" протягом декількох годин при тому, що потужність навантаження склала 2/3 від його заявленої потужності. Несправність виявилася при підключенні імпульсної ЕН до каналу +3В і БП почав відключатися, щойно стрілка амперметра доходила до розподілу 1А. При цьому струми навантаження кожного з інших каналів позитивної напруги не перевищували 3А. Несправною виявилася плата супервізора і була замінена на аналогічну (благо, був такий же БП з силовою частиною, що вигоріла), після чого БП заробив нормально на максимальному струмі, допустимому для використовуваного екземпляра імпульсної ЕН (10А), яка і є предметом опису в даній статті.

Ідея

Ідея створення імпульсного навантаження з'явилася досить давно і вперше була реалізована в 2002 році, але не в теперішньому її вигляді і на іншій елементній базі і для інших цілей і не було на той час для мене особисто достатніх стимулів та інших підстав для розвитку цієї ідеї. Наразі зірки стоять інакше і щось зійшлося для чергового втілення цього пристрою. З іншого боку, пристрій спочатку мало інше призначення - перевірка параметрів імпульсних трансформаторів і дроселів. Але одне одному не заважає. До речі, якщо хтось захоче зайнятися дослідженням індуктивних компонентів за допомогою цього або аналогічного пристрою, будь ласка: нижче за архів статей маститих (в галузі силової електроніки) інженерів, присвячених цій темі.

Отже, що ж є "класична" (аналогова) ЕН у принципі. Струмовий стабілізатор, що працює в режимі короткого замикання. І нічого більше. І буде правий той, хто в пориві будь-якої пристрасті замкне вихідні клеми зарядного пристроюабо зварювального апарату і скаже: це – електронне навантаження! Не факт, звичайно, що подібне замикання не матиме згубних наслідків як для пристроїв, так і для самого оператора, але й той і інший пристрій дійсно є джерелами струму і цілком могли б претендувати після певного доведення на роль електронного навантаження, як і будь-який інший скільки завгодно примітивне джерело струму. Струм аналогової ЕН залежатиме від напруги на виході перевіряється БП, омічного опору каналу польового транзистора, що встановлюється величиною напруги на його затворі.

Струм в імпульсній ЕН залежатиме від суми параметрів до яких буде входити ширина імпульсу, мінімальний опір відкритого каналу вихідного ключа і властивості випробуваного БП (ємність конденсаторів, індуктивність дроселів БП, вихідна напруга).

При відкритому ключі ЕН утворює короткочасне коротке замикання, При якому конденсатори випробуваного БП розряджаються, а дроселі (якщо вони містяться в конструктиві БП) прагнути насичення. Класичного КЗ, проте, немає, т.к. ширина імпульсу обмежена у часі мікросекундними величинами, що визначають величину розрядного струму конденсаторів БП.

У той самий час перевірка імпульсної ЕН є екстремальнішою для проверяемого БП. Зате і "підводних каменів" при такій перевірці виявляється більше, аж до якості провідників, що живлять, підводяться до живильного пристрою. Так, при підключенні імпульсної ЕН до 12-тивольтового БП сполучними мідними проводамидіаметром жили 0,8мм і струмі навантаження 5А, осцилограма на ЕН виявила пульсації, що являють собою послідовність прямокутних імпульсів розмахом до 2В і гострокінцевими викидами з амплітудою, що дорівнює напрузі живлення. На клемах самого БП пульсації від ЕН були відсутні. На самій ЕН пульсації були зведені до мінімуму (менше 50мВ) за допомогою збільшення кількості жил кожного живлячих ЕН провідників - до 6. У "двожильному" варіанті мінімуму пульсацій, порівнянного з "шестижильним", вдалося досягти установкою додаткового електролітичного конденсатора ємністю 4700м живлячих проводів із навантаженням. Отже, при побудові БП, імпульсна ЕН дуже може знадобитися.

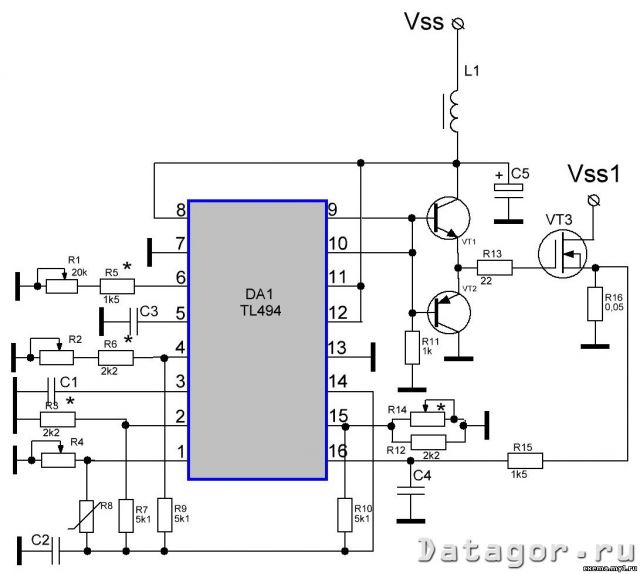

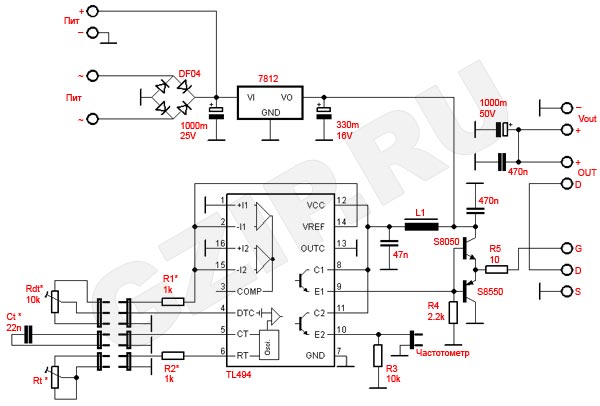

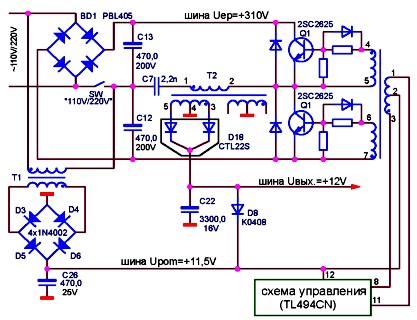

Схема

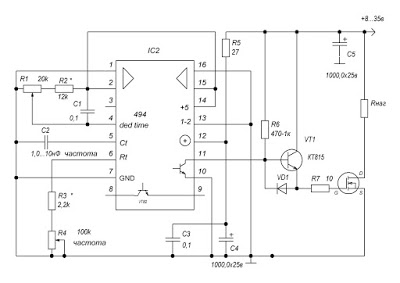

ЕН зібрана на популярних (завдяки велику кількість утилізованих комп'ютерних БП) компонентах. Схема ЕН містить генератор з регульованою частотою і шириною імпульсів, термо-і струмовий захист. Генератор виконаний на ШІМ TL494.

![]()

Регулювання частоти здійснюється змінним резистором R1; шпаруватості - R2; термочутливість - R4; обмеження струму – R14.

Вихід генератора потужний емітерним повторювачем (VT1, VT2) для роботи на ємності затворів польових транзисторів числом від 4-х і більше.

Генераторна частина схеми та буферний каскад на транзисторах VT1, VT2 можуть бути запитані від окремого джерелаживлення з вихідною напругою +12...15В та струмом до 2А або від каналу +12В перевіряється БП.

Вихід ЕН (стік польового транзистора) і з'єднується з "+" перевіряється БП, загальний провід ЕН - із загальним проводом БП. Кожен із затворів польових транзисторів (у разі їх групового використання) повинен бути з'єднаний з виходом буферного каскаду власним резистором, що нівелює різницю параметрів затворів (ємність, гранична напруга) і забезпечує синхронну роботу ключів.

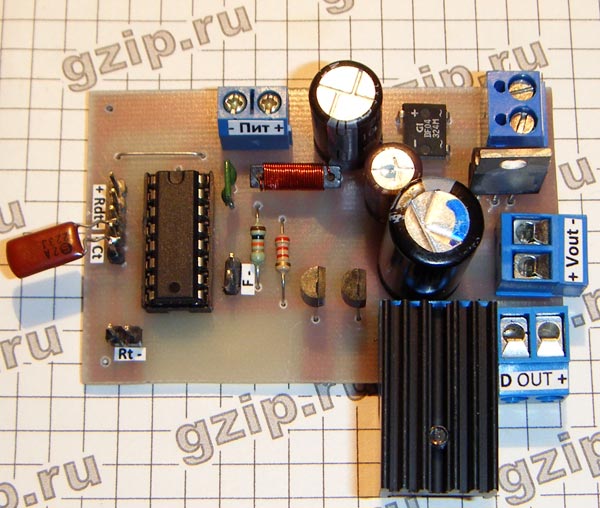

На фотографіях видно, що на платі ЕН є пара світлодіодів: зелений - індикатор живлення навантаження, червоний індикує спрацьовування підсилювачів помилки мікросхеми при критичній температурі (постійне світіння) або обмеження струму (ледь помітне мерехтіння). Роботою червоного світлодіода управляє ключ на транзисторі КТ315, емітер якого з'єднаний із загальним дротом; база (через резистор 5-15кОм) з виведенням 3 мікросхеми; колектор - (через резистор 1,1 кОм) з катодом світлодіода, анод якого з'єднаний з висновками 8, 11, 12 мікросхеми DA1. На схемі цей вузол показаний, т.к. не є обов'язковим.

Щодо резистора R16. При проходженні через нього струму 10А, що розсіюється на резисторі потужність складе 5Вт (при вказаному на схемі опорі). У реальній конструкції використовується резистор опором 0,1 Ом (не виявилося потрібного номіналу) і потужність, що розсіюється на його корпусі при тому струмі, складе 10Вт. Температура резистора при цьому набагато вища за температуру ключів ЕН, які (при використанні радіатора, показаного на фото) гріються не сильно. Тому термодатчик краще встановити на резистори R16 (або в безпосередній близькості), а не на радіаторі з ключами ЕН.

АРХІВ:

Загальний опис та використання

TL 494та її наступні версії - найчастіше застосовувана мікросхема для побудови двотаких перетворювачів живлення.

- TL494 (оригінальна розробка Texas Instruments) - ІС ШІМ перетворювача напруги з однотактними виходами (TL 494 IN - корпус DIP16, -25..85С, TL 494 CN - DIP16, 0..70C).

- К1006ЕУ4 - вітчизняний аналог TL494

- TL594 - аналог TL494 з покращеною точністю підсилювачів помилки та компаратора

- TL598 - аналог TL594 з двотактним (pnp-npn) повторювачем на виході

Справжній матеріал - узагальнення на тему оригінального техдоку Texas Instruments, публікацій International Rectifier ("Силові напівпровідникові прилади International Rectifier", Воронеж, 1999) та Motorola.

Переваги та недоліки даної мікросхеми:

- Плюс: Розвинені ланцюги управління, два диференціальні підсилювачі (можуть виконувати і логічні функції)

- Мінус: Однофазні виходи вимагають додаткового обважування (порівняно з UC3825)

- Мінус: Недоступне струмове керування, відносно повільна петля зворотнього зв'язку(некритично в автомобільних ПН)

- Мінус: Cинронне включення двох і більше ІС не так зручно, як у UC3825

1. Особливості мікросхем TL494

Ланцюги ІОНу та захисту від недонапруги живлення. Схема включається при досягненні живленням порога 5.5..7.0 (типове значення 6.4В). До цього моменту внутрішні шини контролю забороняють роботу генератора та логічної частини схеми. Струм холостого ходу при напрузі живлення +15В (вихідні транзистори відключені) не більше 10 мА. ІОН +5В (+4.75..+5.25 В, стабілізація по виходу не гірше +/- 25мВ) забезпечує струм до 10 мА. Уміщувати ІОН можна лише використовуючи npn-емітерний повторювач (див. TI стор. 19-20), але на виході такого "стабілізатора" напруга сильно залежатиме від струму навантаження.

Генераторвиробляє на часзадающем конденсаторі Сt (висновок 5) пилкоподібна напруга 0..+3.0В (амплітуда задана ІОНом) для TL494 Texas Instruments і 0...+2.8В для TL494 Motorola (чого ж чекати від інших?), відповідно для TI F =1.0/(RtCt), для Мотороли F=1.1/(RtCt).

Допустимі робочі частоти від 1 до 300 кГц, при цьому рекомендований діапазон Rt = 1...500кОм, Ct=470пФ...10мкФ. При цьому типовий температурний дрейф частоти становить (природно без урахування дрейфу навісних компонентів) +/-3%, а догляд частоти в залежності від напруги живлення - в межах 0.1% у всьому допустимому діапазоні.

Для дистанційного вимкнення генератора можна зовнішнім ключем замкнути вхід Rt (6) на вихід ІОНа, або замкнути Ct на землю. Вочевидь, опір витоку розімкнутого ключа має враховуватися за виборі Rt, Ct.

Вхід контролю фази спокою (шпаруватості)через компаратор фази спокою задає необхідну мінімальну паузу між імпульсами у плечах схеми. Це необхідно як недопущення наскрізного струму в силових каскадах поза ІС, так стабільної роботи тригера - час перемикання цифрової частини TL494 становить 200 нс. Вихідний сигнал дозволений тоді, коли пила на Cт перевищує напругу на вході керуючого 4 (DT). На тактових частотах до 150 кГц при нульовому керуючому напрузі фаза спокою = 3% періоду (еквівалентне зміщення керуючого сигналу 100...120 мВ), на великих частотах вбудована корекція розширює фазу спокою до 200...300 нс.

Використовуючи ланцюг входу DT, можна встановити фіксовану фазу спокою (R-R дільник), режим м'якого старту (R-C), дистанційне вимкнення (ключ), а також використовувати DT як лінійний керуючий вхід. Вхідний ланцюг зібраний на pnp-транзисторах, тому вхідний струм (до 1.0 мкА) витікає з ІС, а не втікає в нього. Струм досить великий, тому слід уникати високоомних резисторів (не більше 100 кОм). На TI, стор. 23 наведено приклад захисту від перенапруги з використанням 3-вивідного стабілітрона TL430 (431).

Підсилювачі помилки- Власне, операційні підсилювачі з Ку = 70 ... 95дБ по постійному напрузі (60 дБ для ранніх серій), Ку = 1 на 350 кГц. Вхідні ланцюги зібрані на pnp-транзисторах, тому вхідний струм (до 1.0 мкА) випливає з ІС, а не втікає в неї. Струм досить великий для ОУ, напруга усунення теж (до 10мВ) тому слід уникати високоомних резисторів у керуючих ланцюгах (трохи більше 100 кОм). Зате завдяки використанню pnp-входів діапазон вхідної напруги - від -0.3В до Vживлення-2В.

Виходи двох підсилювачів поєднані діодним АБО. Той підсилювач, на виході якого більша напруга, перехоплює управління логікою При цьому вихідний сигнал доступний не окремо, а тільки з виходу діодного АБО (він же вхід компаратора помилки). Таким чином, тільки один підсилювач може бути замкнений петлею ОС у лінійному режимі. Цей підсилювач і замикає головну, лінійну ОС з вихідної напруги. Другий підсилювач при цьому може використовуватися як компаратор - наприклад, перевищення вихідного струму, або як ключ на логічний сигнал аварії (перегрів, КЗ тощо), дистанційного вимкнення та ін. Один із входів компаратора прив'язується до ІОН, на другому організується логічне АБО аварійних сигналів (ще краще - логічне і сигналів нормальних станів).

З використанням RC частотнозависимой ОС слід пам'ятати, що вихід підсилювачів - фактично однотактний (послідовний діод!), отже заряджати ємність (вгору) він зарядить, а вниз - розряджати буде довго. Напруга на цьому виході знаходиться в межах 0..+3.5В (трохи більше розмаху генератора), далі коефіцієнт напруги різко знижується і приблизно при 4.5В на виході підсилювачі насичуються. Аналогічно, слід уникати низькоомних резисторів у ланцюзі виходу підсилювачів (петлі ОС).

Підсилювачі не призначені для роботи в межах одного такту робочої частоти. При затримці поширення сигналу всередині підсилювача в 400 нс вони для цього дуже повільні, та й логіка управління тригером не дозволяє (виникали б побічні імпульси на виході). У реальних схемах ПН частота зрізу ланцюга ОС вибирається близько 200-10000 Гц.

Тригер та логіка управління виходами- При напрузі живлення не менше 7В, якщо напруга пили на генераторі більша ніж на вході DT, що управляє, і якщо напруга пили більше ніж на будь-якому з підсилювачів помилки (з урахуванням вбудованих порогів і зсувів) - дозволяється вихід схеми. При скиданні генератора з максимуму нуль - виходи відключаються. Тригер з парафазним виходом поділяє частоту надвоє. При логічному 0 на вході 13 (режим виходу) фази тригера об'єднуються АБО і подаються одночасно на обидва виходи, при логічній 1 - подаються парафазно на кожен вихід окремо.

Вихідні транзистори- npn Дарлінгтони з вбудованим тепловим захистом (але без захисту струму). Таким чином, мінімальне падіння напруга між колектором (як правило замкнутим на плюсову шину) та еміттером (на навантаженні) – 1.5В (типове при 200 мА), а у схемі із загальним емітером – трохи краще, 1.1 В типове. Граничний вихідний струм (при одному відкритому транзисторі) обмежений 500 мА, гранична потужність весь кристал - 1Вт.

2. Особливості застосування

Робота на затворі МДП транзистора. Вихідні повторювачі

При роботі на ємнісне навантаження, яким умовно є затвор МДП транзистора, вихідні транзистори TL494 включаються емітерним повторювачем. При обмеженні середнього струму 200 мА схема здатна досить швидко зарядити затвор, але розрядити його вимкненим транзистором неможливо. Розряджати затвор за допомогою заземленого резистора – також незадовільно повільно. Адже напруга на умовній ємності затвора спадає по експоненті, а закриття транзистора затвор треба розрядити від 10В трохи більше 3В. Струм розряду через резистор завжди буде менше струму заряду через транзистор (та й грітися резистор буде неслабко, і красти струм ключа при ході вгору).

Варіант А. Ланцюг розряду через зовнішній pnp транзистор(запозичено на сайті Шихмана - див. "Блок живлення підсилювача Jensen"). При зарядці затвора струм, що протікає через діод, замикає зовнішній pnp-транзистор, при виключенні виходу ІС - замкнений діод, транзистор відкривається і розряджає затвор на землю. Мінус – працює тільки на невеликі ємності навантаження (обмежені струмовим запасом вихідного транзистора ІС).

При використанні TL598 (з двотактним виходом) функція нижнього, розрядного плеча вже зашита на кристалі. Варіант А в цьому випадку недоцільний.

Варіант Б. Незалежний комплементарний повторювач. Оскільки основна струмове навантаженнявідпрацьовується зовнішнім транзистором, ємність (струм заряду) навантаження практично не обмежена. Транзистори та діоди - будь-які ВЧ з невеликою напругою насичення і Cк, і достатнім запасом струму (1А в імпульсі і більше). Наприклад, КТ644+646, КТ972+973. "Земля" повторювача повинна розпаюватися безпосередньо поруч із витоком силового ключа. Колектори транзисторів повторювача обов'язково зашунтувати керамічною ємністю (на схемі не показано).

Яку схему вибрати - залежить насамперед від характеру навантаження (ємність затвора або заряд перемикання), робочої частоти, тимчасових вимог до фронтів імпульсу. А вони (фронти) повинні бути якнайшвидше, адже саме на перехідних процесах на МДП ключі розсіюється більша частина теплових втрат. Рекомендую звернутися до публікацій у збірнику International Rectifier для повного аналізу завдання, а сам обмежусь прикладом.

Потужний транзистор - IRFI1010N - має повний довідковий заряд на затворі Qg=130нКл. Це чимало, адже транзистор має винятково велику площуканалу, щоб забезпечити гранично низький опір каналу (12 мОм). Саме такі ключі і потрібні в 12В перетворювачах, де кожен мільйон на рахунку. Щоб гарантовано відкрити канал, на затворі треба забезпечити Vg=+6В щодо землі, причому повний заряд затвора Qg(Vg)=60нКл. Щоб гарантовано розрядити затвор, заряджений до 10В, треба розсмоктати Qg (Vg) = 90нКл.

2. Реалізація захисту струму, м'якого старту, обмеження шпаруватості

Як правило, у ролі датчика струму так і проситься послідовний резистор у ланцюзі навантаження. Але він крастиме дорогоцінні вольти та вати на виході перетворювача, та й контролюватиме лише ланцюги навантаження, а КЗ у первинних ланцюгах виявити не зможе. Рішення - індуктивний датчик струму первинного ланцюга.

Власне датчик (трансформатор струму) - мініатюрна тороїдальна котушка (внутрішній її діаметр повинен, крім обмотки датчика, вільно пропустити провід первинної обмотки головного силового трансформатора). Крізь тор пропускаємо провід первинної обмотки трансформатора (але не "земляний" провід витоку!). Постійну час наростання детектора задаємо порядку 3-10 періодів тактової частоти, спаду - в 10 разів більше, виходячи зі струму спрацьовування оптрона (порядку 2-10 мА при падінні напруги 1.2-1.6В).

У правій частині схеми - два типові рішення для TL494. Дільник Rdt1-Rdt2 задає максимальну шпаруватість (мінімальну фазу спокою). Наприклад, при Rdt1=4.7кОм, Rdt2=47кОм на виході 4 постійна напруга Udt=450мВ, що відповідає фазі спокою 18..22% (залежно від серії ІВ та робочої частоти).

При включенні живлення Css розряджений і потенціал на вході DT дорівнює Vref (+5В). Сss заряджається через Rss (вона ж Rdt2), плавно опускаючи потенціал DT до нижньої межі, обмеженої дільником. Це "м'який старт". При Css=47мкФ та зазначених резисторах виходи схеми відкриваються через 0.1 с після включення, і виходять на робочу шпару ще протягом 0.3-0.5 с.

У схемі, крім Rdt1, Rdt2, Css присутні два витоку - струм витоку оптрона (не вище 10 мкА при високих температурах, порядку 0.1-1 мкА при кімнатній температурі) і струм входу DT бази вхідного транзистора ІС. Щоб ці струми істотно не впливали на точність дільника, Rdt2=Rss вибираємо не вище 5 кОм, Rdt1 - не вище 100 кОм.

Зрозуміло, вибір саме оптрона та ланцюга DT для управління непринциповий. Можливе використання підсилювача помилки в режимі компаратора, і блокування ємності або резистора генератора (наприклад, тим самим оптроном) - але це саме виключення, а не плавне обмеження.

Тільки найголовніше.

Напруга живлення 8-35в (начебто можна до 40в, але не відчував)

Можливість працювати в однотактному та двотактному режимі.

Для однотактного режиму максимальна тривалість імпульсу становить 96% (щонайменше 4% мертвого часу).

Для двотактного варіанта – тривалість мертвого часу не може бути меншою за 4%.

Подаючи висновок 4 напруга 0…3,3в можна регулювати мертвий час. І здійснювати плавний запуск.

Є вбудований стабілізований джерело опорної напруги 5в та струмом до 10ма.

Є вбудований захист від зниженої напруги живлення, вимикаючись нижче 5,5 ... 7в (найчастіше 6,4в). Біда в тому, що за такої напруги мосфети вже переходять у лінійний режим і згорають.

Є можливість вимкнути генератор мікросхеми замкнувши ключем висновок Rt (6) висновок опорної напруги (14) або виведення Ct (5) на землю.

Робоча частота 1...300кГц.

Два вбудовані операційні підсилювачі «помилки» з коефіцієнтом посилення Ку=70..95Дб. Входи – висновки (1); (2) та (15); (16). Виходи підсилювачів об'єднані елементом АБО, тому той на виході якого напруга більша і керує тривалістю імпульсу. Один із входів компаратора зазвичай прив'язують до опорної напруги (14), а другий – куди треба… Затримка сигналу всередині Підсилювача 400нс, вони не призначені для роботи в межах одного такту.

Вихідні каскади мікросхеми при середньому струмі 200ма, досить швидко заряджають вхідну ємність затвора потужного мосфета, але не забезпечують її розряд. за прийнятний час. У зв'язку з чим обов'язково потрібний зовнішній драйвер.

Висновок (5) кондесатор С2 та висновок (6) резистори R3; R4 – задають частоту внутрішнього генератора мікросхеми. У двотактному режимі вона поділяється на 2.

Є можливість синхронізації, запуск вхідних імпульсів.

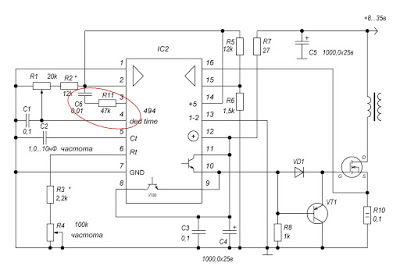

Однотактний генератор з регулюванням частоти та шпаруватості

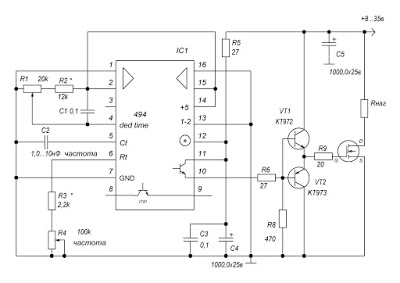

Однотактний генератор з регулюванням частоти та шпаруватості (відношення тривалості імпульсу до тривалості паузи). З одним транзисторним вихідним драйвером. Такий режим реалізується, якщо з'єднати висновок 13 із загальною шиною живлення.

Схема (1)

Оскільки мікросхема має два вихідні каскади, які в даному випадку працюють синфазно, їх для збільшення вихідного струму можна включити паралельно… Або не включати… (зеленим кольором на схемі) Не завжди ставиться і резистор R7.

Вимірюючи операційним підсилювачем напругу на резисторі R10, можна обмежити вихідний струм. На другий вхід подається опорна напруга дільником R5; R6. Ну розумієте, R10 буде грітися.

Ланцюг С6; R11, на (3) ногу, ставлять для більшої стійкості, дата просить, але працює і без неї. Транзистор може взяти і npn структури.

Схема (2)

Схема (3)

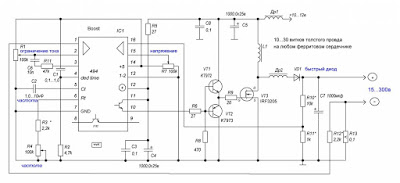

Однотактний генератор з регулюванням частоти та шпаруватості. З двома транзисторним вихідним драйвером (комплементарний повторювач).

Що можу сказати? Форма сигналу краща, скорочуються перехідні процеси в моменти перемикання, вище навантажувальна здатність, менше теплові втрати. Хоча може бути ця суб'єктивна думка. Але. Зараз я використовую лише двох транзисторний драйвер. Так, резистор ланцюга затвора обмежує швидкість перехідних процесів при перемиканні.

Схема (4)

А тут маємо схему типового підвищуючого (boost) регульованого однотактного перетворювача, з регулюванням напруги та обмеженням струму.

Схема робоча, збиралася мною у кількох випадках. Вихідна напруга залежить від кількості витків котушки L1, та й від опору резисторів R7; R10; R11, які під час налагодження підбираються... Саму котушку можна мотати на будь-чому. Розмір – залежно від потужності. Кільце, Ш-сердечник, навіть просто на стрижні. Але вона не повинна входити до насичення. Тому якщо кільце з фериту, то потрібно розрізати та склеїти із зазором. Добре підуть великі кільця з комп'ютерних блоків живлення, їх не треба різати, вони з "розпиленого заліза" зазор вже передбачений. Якщо сердечник Ш-подібний – ставимо не магнітний зазор, бувають із коротким середнім керном – це вже із зазором. Коротше, мотаємо товстим мідним або монтажним дротом(0,5-1,0мм в залежності від потужності) і числом витків 10-і більше (залежно, яку напругу бажаємо отримати). Підключаємо навантаження на заплановану напругу невеликої потужності. Підключаємо наш витвір до акумулятора через потужну лампу. Якщо лампа не спалахнула в повний розжар - беремо вольтметр і осциллограф.

Підбираємо резистори R7; R10; R11 та число витків котушки L1, домагаючись задуманої напруги на навантаженні.

Дросель Др1 - 5...10 витків товстим дротом на будь-якому сердечнику. Бачив навіть варіанти, де L1 та Др1 намотані на одному сердечнику. Сам не перевіряв.

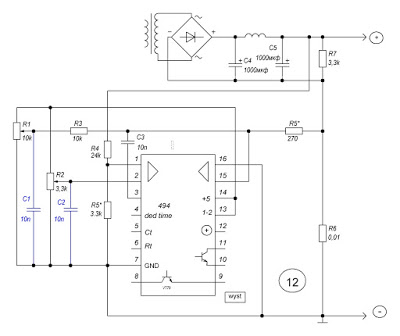

Схема (5)

Це теж реальна схема перетворювача, що підвищує, який можна використовувати, наприклад для зарядки ноутбука від автомобільного акумулятора. Компаратор входів (15);(16) стежить за напругою акумулятора "донора" і відключить перетворювач, коли напруга на ньому впаде нижче обраного порога.

Ланцюг С8; R12; VD2 - так званий Снаббер, призначений придушення індуктивних викидів. Рятує низьковольтний МОСФЕТ, наприклад, IRF3205 витримує, якщо не помиляюся, (стік - витік) до 50в. Проте здорово зменшує ККД. І діод та резистор пристойно гріються. За те зростає надійність. У деяких режимах (схемах) без нього просто згорає потужний транзистор. А буває працює і без цього... Треба дивитися осцилограф...

Схема (6)

Двотактний генератор, що задає.

Різні варіанти виконання та регулювань.

На перший погляд, величезна різноманітність схем включення зводиться до набагато скромнішої кількості дійсно працюючих… Перше, що я зазвичай роблю, коли бачу "хитру" схему – перемальовую у звичному для себе стандарті. Раніше це називалося – ГОСТ. Зараз малюють не зрозуміло як, що дуже ускладнює сприйняття. І приховує помилки. Думаю, часто це робиться спеціально.

Задає генератор для півмосту або мосту. Це найпростіший генератор, тривалість імпульсів і частота регулюється вручну. Оптроном по (3) нозі також можна регулювати тривалість, проте регулювання дуже гостре. Я використав для переривання роботи мікросхеми. Деякі "корифеї" кажуть, що управляти з (3) висновку не можна, мікросхема згорить, але мій досвід підтверджує працездатність цього рішення. До речі, воно вдало використовувалося в зварювальному інверторі.

Схема (10)

Приклади реалізації регулювань (стабілізації) струму та напруги. Те, що малюнку №12 робив сам, - сподобалося. Сині конденсатори, напевно, можна не встановлювати, але краще нехай будуть.

Схема (11)

Генератор на TL494 з регулюванням частоти та шпаруватості

Дуже корисним пристроєм під час проведення експериментів та настроювальних робіт є генератор частоти. Вимоги щодо нього невеликі, потрібні лише:

- регулювання частоти (періоду прямування імпульсів)

- регулювання шпаруватості (коефіцієнт заповнення, довжина імпульсів)

- широкий діапазон

Діапазон регулювання частоти генератора надзвичайно високий – від десятків герц до 500 кГц, а в деяких випадках – і до 1 МГц, залежить від мікросхеми, у різних виробників різні реальні значення максимальної частоти, яку можна "вичавити".

Перейдемо до опису схеми:

Піт± та Піт~ - живлення цифрової частини схеми, постійною та змінною напругою відповідно, 16-20 вольт.

Vout – напруга живлення силової частини, саме воно буде на виході генератора, від 12 вольт. Щоб запитати цифрову частину схеми цієї напруги, необхідно з'єднати Vout і Піт± з урахуванням полярності (від 16 вольт).

OUT(+/D) - силовий вихід генератора, з урахуванням полярності. + - Плюс живлення, D - drain польового транзистора. До них підключається навантаження.

G D S - гвинтова колодка для підключення польового транзистора, який вибирається за параметрами залежно від ваших вимог до частоти та потужності. Розведення друкованої плати виконано з урахуванням мінімальної довжини провідників до вихідного ключа та необхідної їх ширини.

Органи управління:

Rt – змінний резистор управління діапазоном частот генератора, його опір необхідно вибрати під ваші конкретні вимоги. Онлайн калькулятор розрахунку частоти TL494 додається нижче. Резистор R2 обмежує мінімальне значення опору резистора мікросхеми. Його можна підібрати під конкретний екземпляр мікросхеми, а можна ставити таким, як на схемі.

Ct - частотозадавальний конденсатор, відсилання, знову ж таки, до онлайн калькулятору. Дозволяє встановити діапазон регулювання під ваші вимоги.

Rdt – змінний резистор для регулювання шпаруватості. Резистором R1 можна точно підігнати діапазон регулювання від 1% до 99%, також замість нього можна поставити спочатку перемичку.

| Ct, нФ: | |

| R2, ком: | |

| Rt, ком: |

Декілька слів про роботу схеми. Подачею низького рівня 13 виведення мікросхеми (output control) вона переведена в однотактний режим. Нижній схемою транзистор мікросхеми навантажений на резистор R3 для створення виходу для підключення до генератора вимірювача частоти (частотометра). Верхній транзистор мікросхеми керує драйвером на компліментарній парі транзисторів S8050 і S8550, завдання якого - керувати затвором силового вихідного транзистора. Резистор R5 обмежує струм затвора, його значення можна змінювати. Дросель L1 і конденсатор ємністю 47n утворюють фільтр для захисту TL494 від можливих перешкод, створюваних драйвером. Індуктивність дроселя, можливо, слід підібрати під діапазон частот. Слід зазначити, що тразнистори S8050 і S8550 обрані не випадково, оскільки вони мають достатню потужність та швидкість, що забезпечить необхідну крутість фронтів. Як бачите, схема гранично проста, і, водночас, функціональна.

Змінний резистор Rt слід виконати у вигляді двох послідовно з'єднаних резисторів - однооборотного та багатооборотного, якщо вам потрібна плавність та точність регулювання частоти.

Друкована плата, слідуючи традиції, намальована фломастером і витравлена мідним купоросом.

Як силовий транзистор можна використовувати практично будь-які польові транзистори, відповідні за напругою, струмом та частотою. Це може бути: IRF530, IRF630, IRF640, IRF840.

Чим менший опір транзистора у відкритому стані, тим менше він нагріватиметься під час роботи. Тим не менш, наявність радіатора на ньому є обов'язковою.

Зібрано та перевірено за схемою, яку надав flyer.

УПРАВЛІННЯ СИЛОВИМИ КЛЮЧАМИ ІМПУЛЬСНОГО БЛОКУ ЖИВЛЕННЯ

ЗА ДОПОМОГОЮ TL494

СТАТТЯ ПІДГОТОВЛЕНА НА ОСНОВІ КНИГИ А. В. ГОЛОВКОВА та В. Б ЛЮБИЦЬКОГО "БЛОКИ ХАРЧУВАННЯ ДЛЯ СИСТЕМНИХ МОДУЛЕЙ ТИПУ IBM PC-XT/AT"

УПРАВЛЯЮЧА МІКРОСХЕМА TL494

У сучасних ДБЖ для формування керуючого напруги перемикання потужних транзисторівперетворювача зазвичай використовуються спеціалізовані інтегральні мікросхеми(ІМС).

Ідеальна керуюча ІМС для забезпечення нормальної роботи ДБЖ у режимі ШІМ повинна задовольняти більшості з наведених нижче умов:

робоча напругане вище 40В;

наявність високостабільного термостабілізованого джерела опорної напруги;

наявність генератора пилкоподібного напряже-

забезпечення можливості синхронізації зовнішнім сигналом програмованого плавного запуску;

наявність підсилювача сигналу неузгодженості з високою синфазною напругою;

наявність ШІМ-компаратора;

наявність імпульсного керованого тригера;

наявність двоканального передкінцевого каскаду із захистом від КЗ;

наявність логіки придушення подвійного імпульсу;

наявність засобів корекції симетрії вихідної напруги;

наявність струмообмеження в широкому діапазоні синфазної напруги, а також струмообмеження в кожному періоді з відключенням в аварійному режимі;

наявність автоматичного керування з прямою передачею;

забезпечення відключення при зниженні напруги живлення;

забезпечення захисту від перенапруг;

забезпечення сумісності із ТТЛ/КМОП логікою;

забезпечення дистанційного включення та відключення.

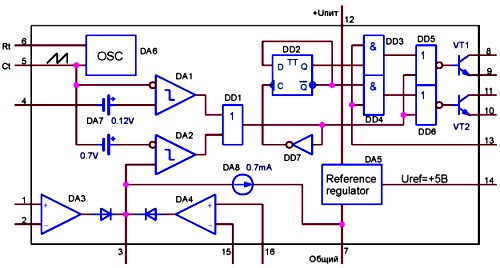

Малюнок 11. Керуюча мікросхема TL494 та її цоколівка.

В якості схеми управління для класу імпульсних блоків живлення, що розглядається, в переважній більшості випадків використовується мікросхема типу TL494CN, що випускається фірмою TEXAS INSTRUMENT (США) (рис.11). Вона реалізує більшість із перелічених вище функцій та випускається поруч зарубіжних фірм під різними найменуваннями. Наприклад, фірма SHARP (Японія) випускає мікросхему IR3M02, фірма FAIRCHILD (США) – UA494, фірма SAMSUNG (Корея) – КА7500, фірма FUJITSU (Японія) – МВ3759 і т.д. Всі ці мікросхеми є повними аналогами вітчизняної мікросхеми КР1114ЕУ4. Розглянемо докладно пристрій та роботу цієї керуючої мікросхеми. Вона спеціально розроблена для управління силовою частиною ДБЖ та містить у своєму складі (рис.12):

Рисунок 12. Функціональна схема ІМС TL494

Генератор пилкоподібної напруги DA6; частота ГПН визначається номіналами резистора і конденсатора, підключених до 5-го і 6-го висновків, і в класі БП, що розглядається, вибирається рівною приблизно 60 кГц;

джерело опорної стабілізованої напруги DA5 (Uref=+5,OB) із зовнішнім виходом (висновок 14);

компаратор "мертвої зони" DA1;

компаратор ШІМ DA2;

підсилювач помилки за напругою DA3;

підсилювач помилки сигналу обмеження струму DA4;

два вихідні транзистори VT1 і VT2 з відкритими колекторами та емітерами;

динамічний двотактний D-тригер у режимі розподілу частоти на 2 - DD2;

допоміжні логічні елементи DD1 (2-АБО), DD3 (2-Й), DD4 (2-Й), DD5 (2-АБО-НЕ), DD6 (2-АБО-НЕ), DD7 (НЕ);

джерело постійної напруги із номіналом 0,1BDA7;

джерело постійного струмуз номіналом 0,7мА DA8.

Схема управління запускатиметься, тобто. на 8 і 11 висновках з'являться послідовності імпульсів у тому випадку, якщо на висновок 12 подати будь-яку напругу живлення, рівень якого знаходиться в діапазоні від +7 до +40 В. Усю сукупність функціональних вузлів, що входять до складу ІМС TL494, можна умовно розбити на цифрову та аналогову частину (цифровий та аналоговий тракти проходження сигналів). До аналогової частини відносяться підсилювачі помилок DA3, DA4, компаратори DA1, DA2, генератор пилкоподібної напруги DA6, а також допоміжні джерела DA5, DA7, DA8. Усі інші елементи, зокрема і вихідні транзистори, утворюють цифрову частину (цифровий тракт).

Рисунок 13. Робота ІМС TL494 у номінальному режимі: U3, U4, U5 – напруги на висновках 3, 4, 5.

Розглянемо спочатку роботу цифрового тракту. Тимчасові діаграми, що пояснюють роботу мікросхеми, наведено на рис. 13. З часових діаграм видно, що моменти появи вихідних керуючих імпульсів мікросхеми, а також їхня тривалість (діаграми 12 і 13) визначаються станом виходу логічного елемента DD1 (діаграма 5). Решта "логіка" виконує лише допоміжну функцію поділу вихідних імпульсів DD1 на два канали. При цьому тривалість вихідних імпульсів мікросхеми визначається тривалістю відкритого стану вихідних транзисторів VT1, VT2. Так як обидва ці транзистори мають відкриті колектори та емітери, то можливе двояке їхнє підключення. При включенні за схемою із загальним емітером вихідні імпульси знімаються із зовнішніх колекторних навантажень транзисторів (з висновків 8 та 11 мікросхеми), а самі імпульси направлені викидами вниз від позитивного рівня (передні фронти імпульсів негативні). Еміттери транзисторів (висновки 9 і 10 мікросхеми) у разі, зазвичай, заземляються. При включенні за схемою із загальним колектором зовнішні навантаження підключаються до емітерів транзисторів і вихідні імпульси, спрямовані в цьому випадку викидами вгору (передні фронти імпульсів позитивні), знімаються з транзисторів емітерів VT1, VT2. Колектори цих транзисторів підключаються до шини живлення мікросхеми (Upom).

Вихідні імпульси інших функціональних вузлів, що входять до складу цифрової частини мікросхеми TL494, спрямовані викидами нагору, незалежно від схеми включення мікросхеми.

Тригер DD2 є двотактним динамічним D-тригером. Принцип його роботи ось у чому. По передньому (позитивному) фронту вихідного імпульсу елемента DD1 стан входу D тригера DD2 записується у внутрішній регістр. Фізично це означає, що перемикається перший із двох тригерів, що входять до складу DD2. Коли імпульс на виході елемента DD1 закінчується, то задньому (негативному) фронту цього імпульсу перемикається другий тригер у складі DD2, і стан виходів DD2 змінюється (на виході Q з'являється інформація, зчитана з входу D). Це виключає можливість появи відпирає імпульсу на основі кожного з транзисторів VT1, VT2 двічі протягом одного періоду. Дійсно, поки рівень імпульсу на вході тригера DD2 не змінився, стан його виходів не зміниться. Тому імпульс передається на вихід мікросхеми по одному з каналів, наприклад, верхньому (DD3, DD5, VT1). Коли імпульс на вході закінчується, тригер DD2 перемикається, замикає верхній і відмикає нижній канал (DD4, DD6, VT2). Тому наступний імпульс, що надходить на вхід і входи DD5, DD6 буде передаватися на вихід мікросхеми по нижньому каналу. Таким чином, кожен з вихідних імпульсів елемента DD1 своїм негативним фронтом перемикає тригер DD2 і цим змінює канал проходження наступного імпульсу. Тож у довідковому матеріалі на керуючу мікросхему вказується, що архітектура мікросхеми забезпечує придушення подвійного імпульсу, тобто. виключає поява двох відпираючих імпульсів на базі одного і того ж транзистора за період.

Розглянемо докладно період роботи цифрового тракту мікросхеми.

Поява відпираючого імпульсу на основі вихідного транзистора верхнього (VT1) або нижнього (VT2) каналу визначається логікою роботи елементів DD5, DD6 ("2АБО-НЕ") та станом елементів DD3, DD4 ("2-І"), яке, у свою чергу , визначається станом тригера DD2

Логіка роботи елемента 2-АБО, як відомо, полягає в тому, що на виході такого елемента з'являється напруга високого рівня(логічна 1) у тому єдиному випадку, якщо на обох його входах присутні низькі рівні напруг (логічні 0). За інших можливих комбінаціях вхідних сигналів на виході елемента 2 АБО-НЕ присутній низький рівень напруги (логічний 0). Тому якщо на виході Q тригера DD2 є логічна 1 (момент ti діаграми 5 рис.13), а на виході /Q - логічний 0, то на обох входах елемента DD3 (2І) виявляться логічні 1 і, отже, логічна 1 з'явиться на виході DD3, отже, і одному з входів елемента DD5 (2АБО-НЕ) верхнього каналу. Отже, незалежно від рівня сигналу, що надходить на другий вхід цього елемента з виходу елемента DD1, станом виходу DD5 буде логічний, і транзистор VT1 залишиться в закритому стані. Станом виходу елемента DD4 буде логічний 0, т.к. логічний 0 присутній одному з входів DD4, надходячи туди з виходу /Q тригера DD2. Логічний 0 з виходу елемента DD4 надходить на один із входів елемента DD6 і забезпечує можливість проходження імпульсу через нижній канал. Цей імпульс позитивної полярності (логічна 1) з'явиться на виході DD6, а значить і на базі VT2 на час паузи між вихідними імпульсами елемента DD1 (тобто на час, коли на виході DD1 є логічний 0 - інтервал trt2 діаграми 5 рис.13 ). Тому транзисгор VT2 відкривається і його колекторі з'являється імпульс викидом вниз від позитивного рівня (у разі включення за схемою із загальним емітером).

Початок наступного вихідного імпульсу елемента DD1 (момент t2 діаграми 5 рис.13) не змінить стану елементів цифрового тракту мікросхеми, крім елемента DD6, на виході якого з'явиться логічний 0, і тому транзистор VT2 закриється. Завершення вихідного імпульсу DD1 (момент ta) зумовить зміну стану виходів тригера DD2 на протилежне (логічний 0 – на виході Q, логічна 1 – на виході /Q). Тому зміниться стан виходів елементів DD3, DD4 (на виході DD3 – логічний 0, на виході DD4 – логічна 1). Пауза, що почалася в момент!3 на виході елемента DD1 зумовить можливість відкривання транзистора VT1 верхнього каналу. Логічний 0 на виході елемента DD3 "підтвердить" цю можливість, перетворюючи її на реальну появу відпирає імпульсу на базі транзистора VT1. Цей імпульс триває до моменту U, після чого VT1 закривається і процеси повторюються.

Таким чином, основна ідея роботи цифрового тракту мікросхеми полягає в тому, що тривалість вихідного імпульсу на висновках 8 і 11 (або на висновках 9 і 10) визначається тривалістю паузи між вихідними імпульсами елемента DD1. Елементи DD3, DD4 визначають канал проходження імпульсу сигналу низького рівня, поява якого чергується на виходах Q і /Q тригера DD2, керованого тим самим елементом DD1. Елементи DD5, DD6 є схеми збігу за низьким рівнем.

Для повноти опису функціональних можливостей мікросхеми слід зазначити ще одну її особливість. Як видно з функціональної схеми малюнку входи елементів DD3, DD4 об'єднані та виведені на висновок 13 мікросхеми. Тому якщо висновок 13 подана логічна 1, то елементи DD3, DD4 працюватимуть як повторювачі інформації з виходів Q і /Q тригера DD2. При цьому елементи DD5, DD6 і транзистори VT1, VT2 будуть перемикатися зі зсувом по фазі на половину періоду, забезпечуючи роботу силової частини ДБЖ, побудованої за двотактною схемою напівмостової. Якщо висновок 13 буде подано логічний 0, то елементи DD3, DD4 будуть заблоковані, тобто. стан виходів цих елементів нічого очікувати змінюватися (постійний логічний 0). Тому вихідні імпульси елемента DD1 впливатимуть на елементи DD5, DD6 однаково. Елементи DD5, DD6, отже, і вихідні транзистори VT1, VT2, будуть перемикатися без зсуву по фазі (одночасно). Такий режим роботи керуючої мікросхеми використовується у разі, якщо силова частина ДБЖ виконана за однотактною схемою. Колектори та емітери обох вихідних транзисторів мікросхеми в цьому випадку поєднуються з метою умощування.

Як "жорстка" логічна одиниця у двотактних схемах використовується вихідна напруга

внутрішнього джерела мікросхеми Uref (висновок 13 мікросхеми поєднується з виведенням 14).

Тепер розглянемо роботу аналогового тракту мікросхеми.

Стан виходу DD1 визначається вихідним сигналом компаратора ШІМ DA2 (діаграма 4), що надходить однією з входів DD1. Вихідний сигнал компаратора DA1 (діаграма 2), що надходить на другий вхід DD1, не впливає у нормальному режимі роботи на стан виходу DD1, який визначається ширшими вихідними імпульсами ШІМ – компаратора DA2.

Крім того, з діаграм рис.13 видно, що при змінах рівня напруги на вході, що не інвертує, ШІМ компаратора (діаграма 3) ширина вихідних імпульсів мікросхеми (діаграми 12, 13) буде пропорційно змінюватися. У нормальному режимі роботи рівень напруги на неінвертуючому вході компаратора ШІМ DA2 визначається тільки вихідною напругою підсилювача помилки DA3 (т.к. вона перевищує вихідну напругу підсилювача DA4), яка залежить від рівня сигналу зворотного зв'язку на його вході, що не інвертує (висновок 1 мікросхеми). Тому при подачі сигналу зворотного зв'язку на виведення 1 мікросхеми ширина вихідних керуючих імпульсів буде змінюватися пропорційно до зміни цього сигналу зворотного зв'язку, який, у свою чергу, змінюється пропорційно змін рівня вихідної напруги ДБЖ, т.к. зворотний зв'язок заводиться саме звідти.

Проміжки часу між вихідними імпульсами на висновках 8 і 11 мікросхеми, коли обидва вихідні транзистори VT1 і VT2 її закриті, називаються "мертвими зонами".

Компаратор DA1 називається компаратором "мертвої зони", т.к. він визначає мінімально можливу її тривалість. Пояснимо це докладніше.

З тимчасових діаграм рис.13 випливає, що якщо ширина вихідних імпульсів ШІМ-комп'ютера DA2 буде в силу будь-яких причин зменшуватися, то починаючи з деякої ширини цих імпульсів вихідні імпульси компаратора DA1 стануть ширшими за вихідні імпульси ШІМ-компаратора DA2 і почнуть визначати стан виходу логічного елемента DD1, отже и. ширину вихідних імпульсів мікросхеми Іншими словами, компаратор DA1 обмежує ширину вихідних імпульсів мікросхеми на певному максимальному рівні. Рівень обмеження визначається потенціалом на неинвенти-рующем вході компаратора DA1 (виведення 4 мікросхеми) в режимі, що встановився. Однак, з іншого боку, потенціал на виведенні 4 визначатиме діапазон широтного регулювання вихідних імпульсів мікросхеми. При збільшенні потенціалу висновку 4 цей діапазон звужується. Найширший діапазон регулювання виходить тоді, коли потенціал на виведенні 4 дорівнює 0.

Однак у цьому випадку виникає небезпека, пов'язана з тим, що ширина "мертвої зони" може стати рівною 0 (наприклад, у разі значного зростання споживаного ДБЖ струму). Це означає, що керуючі імпульси на висновках 8 і 11 мікросхеми слідуватимуть безпосередньо один за одним. Тому може виникнути ситуація, відома під назвою "пробою по стійці". Вона пояснюється інерційністю силових транзисторів інвертора, які можуть відкриватися і закриватися миттєво. Тому, якщо одночасно на базу відкритого до цього транзистора подати замикаючий сигнал, а на базу закритого транзистора - отпирающий (тобто з нульовою "мертвою зоною"), то вийде ситуація, коли один транзистор ще не закрився, а інший вже відкритий. Тоді і виникає пробій по транзисторній стійці напівмосту, який полягає у протіканні наскрізного струму через обидва транзистори. Струм цей, як видно із схеми рис. 5, мине первинну обмотку силового трансформатора і практично нічим не обмежений. Захист струму у разі не працює, т.к. Струм не протікає через струмовий датчик (на схемі не показаний; конструкція і принцип дії застосовуваних струмових датчиків будуть докладно розглянуті в наступних розділах), а значить, цей датчик не може видати сигнал на схему управління. Тому наскрізний струм досягає великої величини за дуже короткий проміжок часу. Це призводить до різкого зростання потужності, що виділяється на обох силових транзисторах, і практично миттєвого виходу їх з ладу (як правило, пробій). Крім того, кидком наскрізного струму можуть бути виведені з ладу діоди силового моста, що випрямляє. Цей процес закінчується перегоранням мережного запобіжника, який через свою інерційність не встигає захистити елементи схеми, а лише захищає від навантаження первинну мережу.

Тому керуюча напруга; подане на бази силових транзисторів має бути сформовано таким чином, щоб спочатку надійно закривався один із цих транзисторів, а вже потім відкривався б інший. Іншими словами, між керуючими імпульсами, що подаються на бази силових транзисторів обов'язково повинен бути тимчасовий зсув, не рівний нулю ("мертва зона"). Мінімальна допустима тривалість "мертвої зони" визначається інерційністю застосовуваних як силові ключі транзисторів.

Архітектура мікросхеми дозволяє регулювати величину мінімальної тривалості "мертвої зони" за допомогою потенціалу виведення 4 мікросхеми. Потенціал цей визначається за допомогою зовнішнього дільника, що підключається до шини вихідної напруги внутрішнього опорного джерела мікросхеми Uref.

У деяких варіантах ДБЖ такий дільник відсутній. Це означає, що після завершення процесу плавного пуску (див. нижче) потенціал на виведенні 4 мікросхеми стає рівним 0. У цих випадках мінімально можлива тривалість "мертвої зони" все ж таки не стане рівною 0, а визначатиметься внутрішнім джерелом напруги DA7 (0, 1В), який підключений до неінвертуючого входу компаратора DA1 своїм позитивним полюсом, і висновку 4 мікросхеми - негативним. Таким чином, завдяки включенню цього джерела ширина вихідного імпульсу компаратора DA1, а значить і ширина "мертвої зони", за жодних умов не може стати рівною 0, а значить "пробою по стійці" буде неможливий. Іншими словами, в архітектуру мікросхеми закладено обмеження максимальної тривалості її вихідного імпульсу (мінімальної тривалості "мертвої зони"). Якщо є дільник, підключений до виведення 4 мікросхеми, то після плавного пуску потенціал цього виводу не дорівнює 0, тому ширина вихідних імпульсів компаратора DA1 визначається не тільки внутрішнім джерелом DA7, а й залишковим (після завершення процесу плавного запуску) потенціалом на виведенні 4. при цьому, як було зазначено вище, звужується динамічний діапазон широтного регулювання ШІМ компаратора DA2.

СХЕМА ПУСКУ

Схема пуску призначена для отримання напруги, яким можна було б запитати керуючу мікросхему з метою її запуску після включення ШВП в мережу живлення. Тому під пуском мається на увазі запуск у роботу в першу чергу керуючої мікросхеми, без нормального функціонування якої неможлива робота силової частини та всієї схеми ДБЖ загалом.

Схема пуску може бути побудована двома різними способами:

із самозбудженням;

із примусовим збудженням.

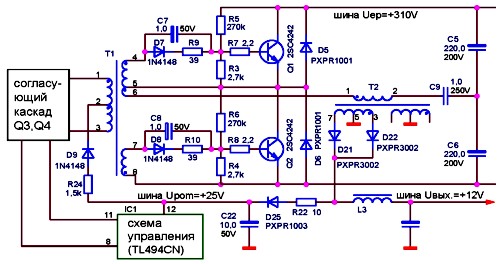

Схема із самозбудженням використовується, наприклад, в ДБЖ GT-150W (рис.14). Випрямлена напруга мережі Uep подається на резистивний дільник R5, R3, R6, R4, який є базовим для обох ключових силових транзисторів Q1, Q2. Тому через транзистори під впливом сумарної напруги на конденсаторах С5, С6 (Uep) починає протікати базовий струмпо ланцюгу (+) С5 - R5 - R7 - 6-е Q1 - R6 - R8 - 6-е Q2 - "загальний провід" первинної сторони - (-) С6.

Обидва транзистори відкриваються цим струмом. В результаті через ділянки колектор-емітер обох транзисторів починають протікати струми взаємно протилежних напрямків по ланцюгах:

через Q1: (+) С5 - шина +310 В - к-е Q1 - 5-6 Т1 -1-2 Т2-С9- (-) С5.

через Q2: (+) С6 - С9 - 2-1 Т2 - 6-5 Т1 - к-е Q2 - "загальний провід" первинної сторони - (-) С6.

Малюнок 14. Схема запуску із самозбудженням ДБЖ GT-150W.

Якби обидва струми, що протікають через додаткові (пускові) витки 5-6 Т1 у протилежних напрямках, були б рівні, то результуючий струм дорівнював би 0, і схема не змогла б запуститися.

Проте з технологічного розкиду коефіцієнтів посилення струму транзисторів Q1, Q2 завжди якийсь із цих струмів більше іншого, т.к. транзистори відкриті різною мірою. Тому результуючий струм через витки 5-6 Т1 не дорівнює 0 і має той чи інший напрямок. Припустимо, що переважає струм через транзистор Q1 (тобто Q1 відкритий більшою мірою, ніж Q2) і, отже, струм протікає у бік від виведення 5 до виведення 6 Т1. Подальші міркування ґрунтуються на цьому припущенні.

Однак, заради справедливості слід зазначити, що переважним може виявитися і струм через транзистор Q2, і тоді всі описані процеси будуть ставитися до транзистора Q2.

Протікання струму через витки 5-6 Т1 викликає виникнення ЕРС взаємоіндукції на всіх обмотках керуючого трансформатора Т1. При цьому (+) ЕРС виникає на висновку 4 щодо виведення 5 і в базу Q1 під впливом цієї ЕРС тече додатково струм, що його відкриває по ланцюгу: 4 Т1 - D7-R9-R7-6-3 Q1 - 5 Т1.

Одночасно на виведенні 7 Т1 з'являється (-) ЕРС щодо виведення 8, тобто. полярність цієї ЕРС виявляється замикає Q2 і він закривається. Далі набуває чинності позитивний зворотний зв'язок (ПОС). Дія її полягає в тому, що при зростанні струму через ділянку колектор-емітер Q1 і витки 5-6 Т1 на обмотці 4-5 Т1 діє зростаюча ЕРС, яка, створюючи додатковий базовий струм для Q1, ще більшою мірою відкриває його. Процес цей розвивається лавиноподібно (дуже швидко) і призводить до повного відкривання Q1 та замикання Q2. Через відкритий Q1 і первинну обмотку 1-2 силового імпульсного трансформатора Т2 починає протікати струм, що лінійно наростає, що викликає появу імпульсу ЕРС взаємоіндукції на всіх обмотках Т2. Імпульс з обмотки 7-5 Т2 заряджає накопичувальну ємність С22. На С22 з'являється напруга, яка подається як живильного на висновок 12 керуючої мікросхеми IC1 типу TL494 і на каскад. Мікросхема запускається і генерує на своїх висновках 11, 8 прямокутні послідовності імпульсів, якими через каскад (Q3, Q4, Т1) починають перемикатися силові ключі Q1, Q2. На всіх обмотках силового трансформатора Т2 виникають імпульсні ЕРС номінального рівня. У цьому ЭРС з обмоток 3-5 і 7-5 постійно підживлюють С22, підтримуючи у ньому постійний рівень напруги (близько +27В). Іншими словами, мікросхема по кільцю зворотного зв'язку починає запитувати сама себе (самопідживлення). Блок виходить на робочий режим. Напруга живлення мікросхеми та узгоджувального каскаду є допоміжною, діє тільки всередині блоку і зазвичай називається Upom.

Ця схема може мати деякі різновиди, як, наприклад, в імпульсному блоці живлення LPS-02-150XT (виробництво Тайвань) для комп'ютера Мазовія СМ1914 (рис.15). У цій схемі початковий поштовх для розвитку процесу запуску виходить за допомогою окремого однопівперіодного випрямляча D1, С7, який запитує перший позитивний півперіод мережі базовий для силових ключів резистивний дільник. Це прискорює запуску, т.к. первісне відмикання одного з ключів відбувається паралельно із зарядкою згладжуючих конденсаторів великої ємності. В іншому схема працює аналогічно до розглянутої вище.

Рисунок 15. Схема запуску із самозбудженням в імпульсному блоці живлення LPS-02-150XT

Така схема використовується, наприклад, в ДБЖ PS-200B фірми LING YIN GROUP (Тайвань).

Первинна обмотка спеціального пускового трансформатора Т1 включається на половину напруга мережі (при номіналі 220В) або на повну (при номіналі 110В). Це робиться з тих міркувань, щоб амплітуда змінної напруги на вторинній обмотці Т1 не залежала б від номіналу мережі живлення. Через первинну обмотку Т1 при включенні ДБЖ у мережу протікає змінний струм. На вторинній обмотці 3-4 Т1 тому наводиться змінна синусоїдальна ЕРС з частотою мережі живлення. Струм, що протікає під впливом цієї ЕРС, випрямляється спеціальною схемою мостової на діодах D3-D6 і згладжується конденсатором С26. На С26 виділяється постійна напруга близько 10-11В, яке подається як живильний на висновок 12 керуючої мікросхеми U1 типу TL494 і на каскад. Паралельно з цим процесом відбувається заряд конденсаторів фільтра, що згладжує. Тому на момент подачі харчування на мікросхему силовий каскад також виявляється запитаним. Мікросхема запускається і починає генерувати на своїх висновках 8, 11 послідовності прямокутних імпульсів, якими через каскад, що узгоджує, починають перемикатися силові ключі. В результаті з'являються вихідні напруги блоку. Після виходу на режим самопідживлення мікросхеми проводиться з шини вихідної напруги +12В через діод D8, що розв'язує. Так як ця напруга самопідживлення трохи перевищує вихідну напругу випрямляча D3-D5, то діоди цього пускового випрямляча замикаються, і він надалі не впливає на роботу схеми.

Необхідність зворотного зв'язку через діод D8 не є обов'язковою. У схемах деяких ДБЖ, де застосовується примусове порушення, такий зв'язок відсутня. Керуюча мікросхема та узгоджуючий каскад протягом усього часу роботи запитуються з виходу пускового випрямляча. Однак рівень пульсації на шині Upom у цьому випадку виходить дещо більшим, ніж у разі живлення мікросхеми з шини вихідної напруги +12В.

Підсумовуючи описи схем запуску, можна назвати основні особливості їх побудови. У схемі із самозбудженням проводиться початкове перемикання силових транзисторів, результатом чого є поява напруги живлення мікросхеми Upom. У схемі з примусовим збудженням спочатку отримують Upom, а вже як результат – перемикання силових транзисторів. Крім того, у схемах із самозбудженням напруга Upom зазвичай має рівень близько +26В, а у схемах із примусовим збудженням - близько +12В.

Схема з примусовим збудженням (з окремим трансформатором) наведено на рис.16.

Рисунок 16. Схема запуску із примусовим збудженням імпульсного блокуживлення PS-200B (LING YIN GROUP).

УГОДНИЙ КАСКАД ІМПУЛЬСНОГО БЛОКУ ЖИВЛЕННЯ

Для узгодження та розв'язки потужного вихідного каскаду від малопотужних ланцюгів управління служить узгоджуючий каскад.

Практичні схеми побудови узгоджувального каскаду в різних ДБЖ можна поділити на два основні варіанти:

транзисторний варіант, де як ключі використовуються зовнішні транзистори в дискретному виконанні;

бестранзисторний варіант, де як ключі використовуються вихідні транзистори самої керуючої мікросхеми VT1, VT2 (в інтегральному виконанні).

Крім того, ще однією ознакою, за якою можна класифікувати узгоджувальні каскади, є спосіб управління силовими транзистораминапівмостового інвертора. За цією ознакою всі узгоджувальні каскади можна поділити на:

каскади із загальним управлінням, де управління обома силовими транзисторами проводиться за допомогою одного загального для них керуючого трансформатора, який має одну первинну і дві вторинні обмотки;

каскади з роздільним управлінням, де керування кожним із силових транзисторів виробляється з допомогою окремого трансформатора, тобто. у погодному каскаді є два управляючі трансформатори.

Виходячи з обох класифікацій узгоджуючий каскад може бути виконаний одним із чотирьох способів:

транзисторний із загальним управлінням;

транзисторний із роздільним управлінням;

бестранзисторний із загальним управлінням;

бестранзисторний із роздільним управлінням.

Транзисторні каскади з роздільним управлінням використовуються рідко, або взагалі не використовуються. Авторам не довелося зіткнутися з таким варіантом виконання каскаду. Інші три варіанти зустрічаються більш менш часто.

У всіх випадках зв'язок із силовим каскадом здійснюється трансформаторним методом.

При цьому трансформатор виконує дві основні функції: посилення керуючого сигналу струму (за рахунок ослаблення напруги) і гальванічної розв'язки. Гальванічна розв'язка необхідна тому, що керуюча мікросхема і каскад, що узгоджують, знаходяться на вторинній стороні, а силовий каскад - на первинній стороні ДБЖ.

Розглянемо роботу кожного зі згаданих варіантів узгоджувального каскаду на конкретних прикладах.

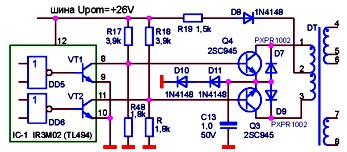

У транзисторній схемі із загальним управлінням як узгоджувальний каскад використовується двотактний трансформаторний попередній підсилювач потужності на транзисторах Q3 і Q4 (рис.17).

Рисунок 17. Погоджувальний каскад імпульсного блоку живлення KYP-150W ( транзисторна схемаіз загальним управлінням).

Рисунок 18. Реальна форма імпульсів на колекторах

Струми через діоди D7 і D9, що протікають під впливом магнітної енергії, запасеної в сердечнику DT, мають вигляд експонентів, що спадають. У сердечнику DT під час протікання струмів через діоди D7 і D9 діє змінний (спадаючий) магнітний потік, що і зумовлює появу імпульсів ЕРС на його вторинних обмотках.

Діод D8 усуває вплив каскаду на керуючу мікросхему через загальну шину живлення.

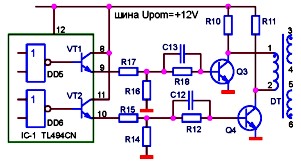

Інший різновид транзисторного узгоджувального каскаду із загальним управлінням використовується в імпульсному блоці живлення ESAN ESP-1003R (рис.19). Першою особливістю цього варіанта є те, що вихідні транзистори VT1, VT2 мікросхеми включені як емітерні повторювачі. Вихідні сигнали знімаються з 9 висновків, 10 мікросхеми. Резистори R17, R16 і R15, R14 є емітерними навантаженнями транзисторів VT1 і VT2 відповідно. Ці ж резистори утворюють базові дільники для транзисторів Q3, Q4, які працюють у ключовому режимі. Ємності С13 та С12 є форсуючими та сприяють прискоренню процесів перемикання транзисторів Q3, Q4. Другий характерною особливістюцього каскаду і те, що первинна обмотка керуючого трансформатора DT немає висновку від середньої точки і підключена між колекторами транзисторів Q3, Q4. Коли вихідний транзистор VT1 керуючої мікросхеми відкривається, то опиняється напругою Upom базовий для транзистора Q3 дільник R17, R16. Тому через керуючий перехід Q3 протікає струм і він відкривається. Прискоренню цього процесу сприяє форсуюча ємність С13, яка забезпечує подачу в базу Q3 струму, що відмикає, в 2-2,5 рази перевищує встановилося значення. Результатом відкривання Q3 є те, що первинна обмотка 1-2 DT своїм виведенням 1 підключається до корпусу. Так як другий транзистор Q4 замкнений, то через первинну обмотку DT починає протікати струм, що наростає, по ланцюгу: Upom - R11 - 2-1 DT - до-е Q3 - корпус.

Рисунок 19. Узгоджуючий каскад імпульсного блоку живлення ESP-1003R ESAN ELECTRONIC CO., LTD (транзисторна схема із загальним керуванням).

На вторинних обмотках 3-4 та 5-6 DT з'являються імпульси ЕРС прямокутної форми. Напрямок намотування вторинних обмоток DT різний. Тому один із силових транзисторів (на схемі не показано) отримає базовий імпульс, що відкриває, а інший - закриває. Коли VT1 керуючої мікросхеми різко закривається, слідом за ним також різко закривається і Q3. Прискорення процесу закривання сприяє форсуюча ємність С13, напруга з якої прикладається до переходу база-емітер Q3 в полярності, що закриває. Далі триває "мертва зона", коли обидва вихідні транзистори мікросхеми закриті. Далі відкривається вихідний транзистор VT2, отже виявляється запитаним напругою Upom базовий другого транзистора Q4 дільник R15, R14. Тому Q4 відкривається і первинна обмотка 1-2 DT виявляється підключена до корпусу іншим своїм кінцем (висновком 2), тому через неї починає протікати наростаючий струм протилежного попереднього випадку напрямку по ланцюгу: Upom -R10- 1-2 DT - к-е Q4 - "корпус".

Тому полярність імпульсів на вторинних обмотках DT змінюється, і що відкриває імпульс отримає другий силовий транзистор, але в основі першого діятиме імпульс закриває полярності. Коли VT2 керуючої мікросхеми різко закривається, слідом за ним також різко закривається Q4 (за допомогою форсуючої ємності С12). Далі знову триває "мертва зона", після чого процеси повторюються.

Таким чином, основна ідея, закладена в роботу цього каскаду, полягає в тому, що змінний магнітний потік у сердечнику DT вдається отримати завдяки тому, що первинна обмотка DT підключається до корпусу одним, то іншим своїм кінцем. Тому через неї протікає змінний струм без постійної складової при однополярному живленні.

У бестранзисторних варіантах узгоджувальних каскадів ДБЖ як транзисторів узгоджувального каскаду, як це було зазначено раніше, використовуються вихідні транзистори VT1, VT2 керуючої мікросхеми. В цьому випадку дискретні транзистори узгоджувального каскаду відсутні.

Бестранзисторна схема із загальним управлінням використовується, наприклад, у схемі ДБЖ PS-200В. Вихідні транзистори мікросхеми VT1, VT2 навантажуються колекторами первинними напівобмотками трансформатора DT (рис.20). Живлення подається до середньої точки первинної обмотки DT.

Рисунок 20. Погоджувальний каскад імпульсного блоку живлення PS-200B (бестранзисторна схема із загальним керуванням).

Коли відкривається транзистор VT1, то струм, що наростає, протікає через цей транзистор і напівобмотку 1-2 керуючого трансформатора DT. На вторинних обмотках DT з'являються керуючі імпульси, що мають таку полярність, що один із силових транзисторів інвертора відкривається, а інший закривається. Після закінчення імпульсу VT1 різко закривається, струм через напівобмотку 1-2 DT перестає протікати, тому зникає ЕРС на вторинних обмотках DT, що призводить до закривання силових транзисторів. Далі триває "мертва зона", коли обидва вихідні транзистори VT1, VT2 мікросхеми закриті, і струм через первинну обмотку DT не протікає. Далі відкривається транзистор VT2, струм, наростаючи в часі, протікає через цей транзистор і напівобмотку 2-3 DT. Магнітний потік, створюваний цим струмом у сердечнику DT, має протилежне попередньому випадку напрямок. Тому на вторинних обмотках DT наводяться ЕРС протилежної попередньому випадку полярності. В результаті відкривається другий транзистор напівмостового інвертора, а на базі першого імпульс має закриває його полярність. Коли VT2 керуючої мікросхеми закривається, струм через нього та первинну обмотку DT припиняється. Тому зникають ЕРС на вторинних обмотках DT, і силові транзистори інвертора знову закриті. Далі знову триває "мертва зона", після чого процеси повторюються.

Основна ідея побудови цього каскаду полягає в тому, що змінний магнітний потік в сердечнику трансформатора, що управляє, вдається отримати завдяки подачі харчування в середню точку первинної обмотки цього трансформатора. Тому струми протікають через напівобмотки з однаковим числом витків у різних напрямках. Коли обидва вихідні транзистори мікросхеми закриті ("мертві зони"), магнітний потік у сердечнику DT дорівнює 0. Почергове відкривання транзисторів викликає почергову появу магнітного потоку то однієї, то іншої напівобмотки. Результуючий магнітний потік у сердечнику виходить змінним.

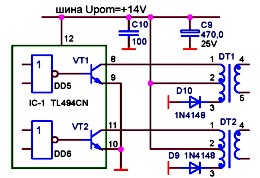

Останній із зазначених різновидів (бестранзисторна схема з роздільним управлінням) використовується, наприклад, в ДБЖ комп'ютера Appis (Перу). У цій схемі є два управляючі трансформатори DT1, DT2, первинні напівобмотки яких є колекторними навантаженнями для вихідних транзисторів мікросхеми (рис.21). У цій схемі керування кожним із двох силових ключів здійснюється через окремий трансформатор. Живлення подається на колектори вихідних транзисторів мікросхеми із загальної шини Upom через середні точки первинних обмоток управляючих трансформаторів DT1, DT2.

Діоди D9, D10 з відповідними частинами первинних обмоток DT1, DT2 утворюють схеми розмагнічування сердечників. Зупинимося на цьому питанні докладніше.

Рисунок 21. Погоджувальний каскад імпульсного блоку живлення "Appis" (бестранзисторна схема з роздільним управлінням).

Узгоджуючий каскад (рис.21) насправді є два незалежних однотактних прямоходових перетворювача, т.к. відкриває струм протікає основою силового транзистора під час відкритого стану узгоджувального транзистора, тобто. узгоджуючий та пов'язаний з ним через трансформатор силовий транзистор відкриті одночасно. При цьому обидва імпульсного трансформатора DT1, DT2 працюють із постійною складовою струму первинної обмотки, тобто. з вимушеним підмагнічуванням. Якщо не передбачити спеціальних заходів з розмагнічування сердечників, то вони увійдуть у магнітне насичення за кілька періодів роботи перетворювача, що призведе до значного зменшення індуктивності первинних обмоток і виходу з ладу транзисторів VT1, VT2, що перемикають. Розглянемо процеси, які у перетворювачі на транзисторі VT1 і трансформаторі DT1. Коли транзистор VT1 відкривається, через нього і первинну обмотку 1-2 DT1 протікає струм, що лінійно наростає, по ланцюгу: Upom -2-1 DT1 - к-е VT1 - "корпус".

Коли отпирающий імпульс з урахуванням VT1 закінчується, він різко закривається. Струм через обмотку 1-2 DT1 припиняється. Однак ЕРС на обмотці 2-3 DT1 при цьому змінює полярність, і через цю обмотку і діод D10 протікає розмагнічуючий сердечник DT1 струм по ланцюгу: 2 DT1 - Upom - С9- "корпус"- D10-3DT1.

Струм цей - лінійно спадаючий, тобто. похідна магнітного потоку через сердечник DT1 змінює знак, і сердечник розмагнічується. Таким чином, під час цього зворотного такту відбувається повернення надлишкової енергії, запасеної в сердечнику DT1 за час відкритого стану транзистора VT1, в джерело (заряджається накопичувальний конденсатор С9 шини Upom).

Однак такий варіант реалізації каскаду, що погоджує, найменш переважний, т.к. обидва трансформатори DT1, DT2 працюють з недовикористанням по індукції та з постійною складовою струму первинної обмотки. Перемагнічування сердечників DT1, DT2 відбувається за приватним циклом, що охоплює лише позитивні значення індукції. Магнітні потоки в осердях через це виходять пульсуючими, тобто. містять постійну складову. Це призводить до завищених масогабаритних показників трансформаторів DT1, DT2 і, крім того, в порівнянні з іншими варіантами узгоджувального каскаду, тут потрібно два трансформатори замість одного.

| ОСНОВНІ ПАРАМЕТРИ ІМПУЛЬСНИХ БЛОКІВ ЖИВЛЕННЯ ДЛЯ IBM | Розглядаються основні параметри імпульсних блоків живлення, наведено цоколівку роз'єму, принцип роботи від напруги мережі 110 і 220 вольт, | |||

| Детально розписана мікросхема TL494, схема включення та варіанти використання для керування силовими ключами імпульсних блоків живлення. | ||||

| УПРАВЛІННЯ СИЛОВИМИ КЛЮЧАМИ ІМПУЛЬСНОГО БЛОКУ ЖИВЛЕННЯ ЗА ДОПОМОГОЮ TL494 | Описано основні способи управління базовими ланцюгами силових транзисторів імпульсних блоків живлення, варіанти побудови вторинного живлення. | Повний опис принципової схемита її роботи імпульсного блоку живлення | ||